# Design Considerations for Integrated Semiconductor Control Electronics for a Large-scale Solid State Quantum Processor

Hendrik Bluhm

Andre Kruth

Lotte Geck

Carsten Degenhardt

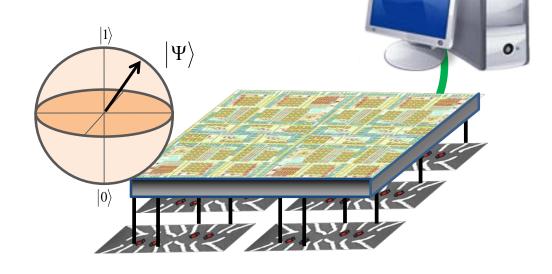

# **Quantum Computing**

### **Classical bits**

0 or 1

### **Quantum bits**

$\alpha | 0 \rangle + \beta | 1 \rangle$

N bits =>  $2^N$  states 0, 1, ...,  $2^{N}-1$

N qubits:  $2^N$  dimensional Hilbert space  $|0\rangle$ ,  $|1\rangle$ , ...,  $|2^N-1\rangle$

### **Principles of quantum mechanics**

- ⇒Huge memory space

- ⇒Built-in parallelism

- ⇒ **Exponential speedup** (for some problems)

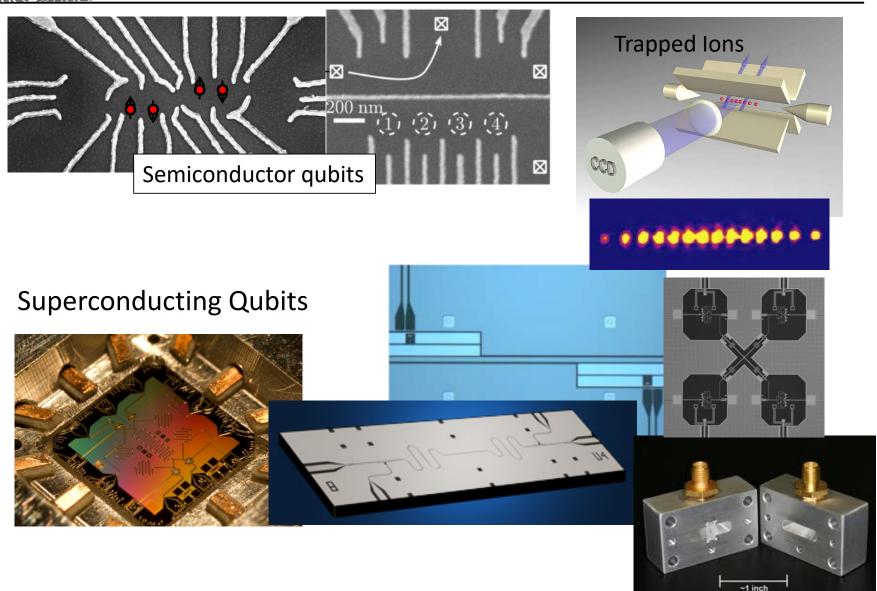

# Qubit Zoo

# Scaling Need for Applications

# Prime factorization and decryption

### **Predicted resource requirement**

5 x 10<sup>8</sup> qubits, 1 day for 1024 bit number

### **Quantum Chemistry**

$10^8$  qubits, 13 days for  $C_3H_7NO_2$  $10^6$  qubits for  $Fe_2S_2$

- Catalyst design for CO<sub>2</sub> capture or fertilizer production

- Quantum material design

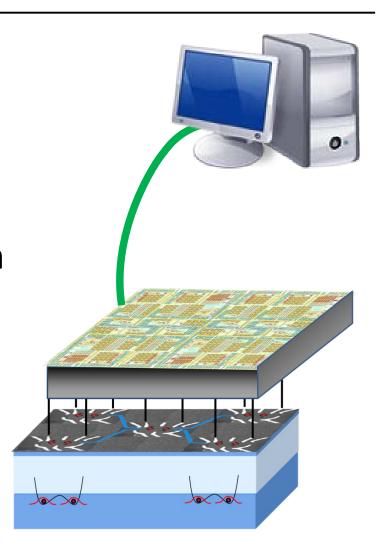

# Quantum Computing Architecture

### Requirements for surface-code error correction

- Lattice 2D nearest neighbor interaction

- Error rate < 10<sup>-3</sup>

### Resource needs for high impact computations

- 10000 logical, error corrected qubits

- x 1000 physical qubits per logical qubit

- x 10 overhead to work around drawbacks of error correction

- $rac{10^8}{10^8}$  qubits

Requirements for scalable quantum computing

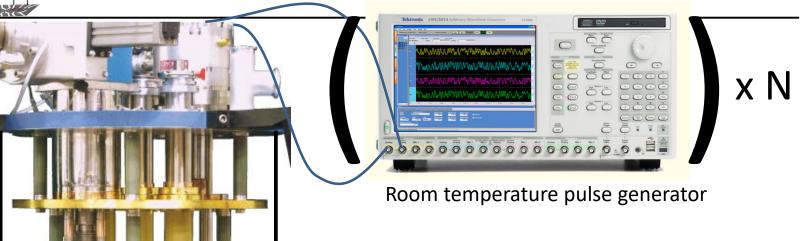

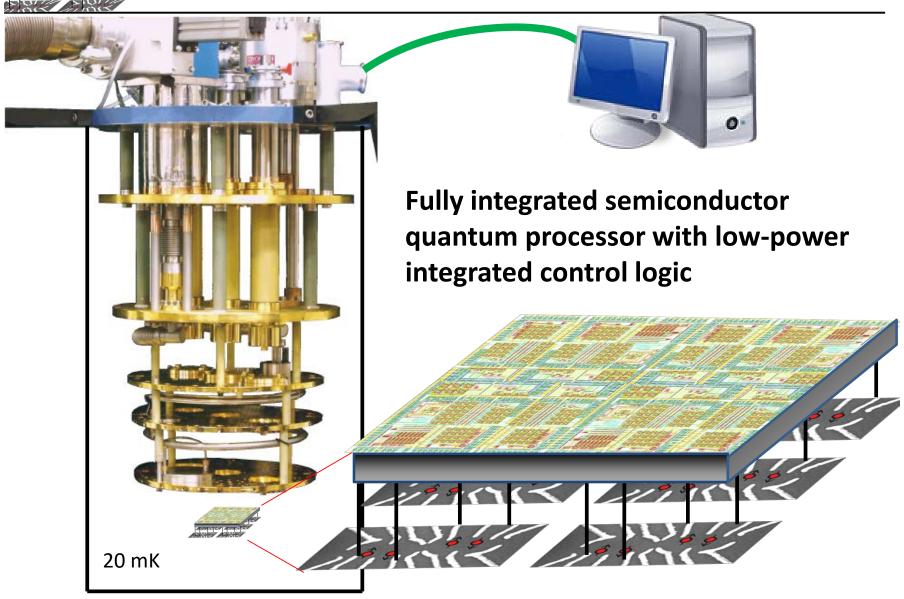

Vision of a scalable quantum processor

Ultra-low power control electronics

### **Scaling limitations**

### **Control electronics**

Thousands of racks

### Wiring

1 coax cable per qubit => 1 m<sup>2</sup> scale wiring cross section for 10<sup>6</sup> qubits

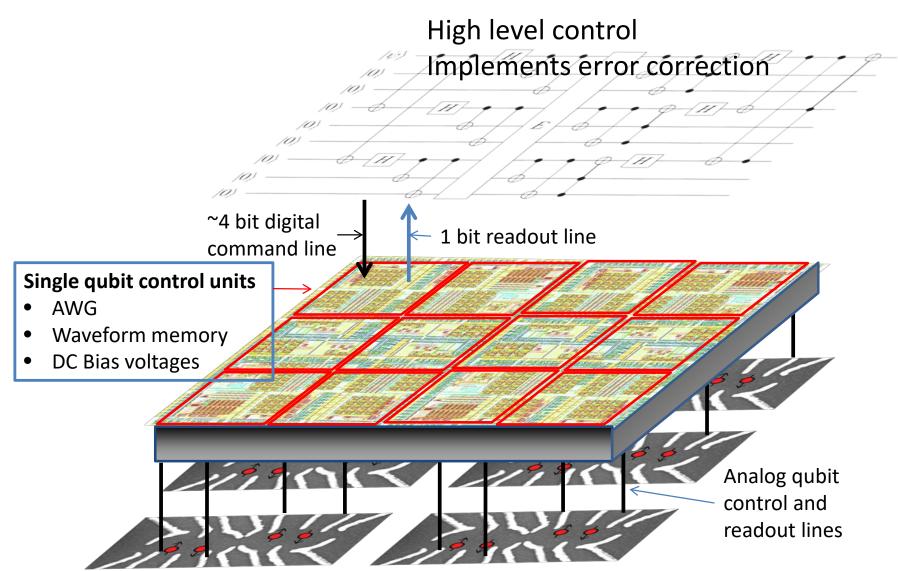

# Vision of a Scalable QC

### Low Level Architecture

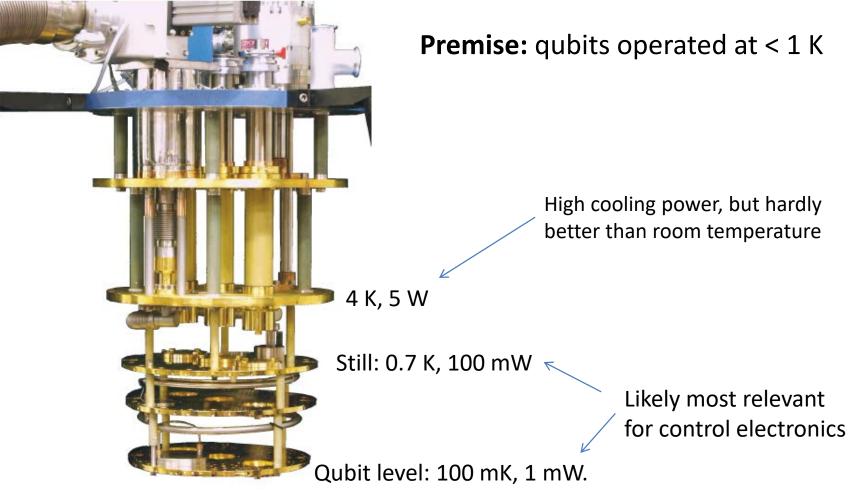

# (Cooling) Power Budget

=> Can dissipate at most a few nW per qubit

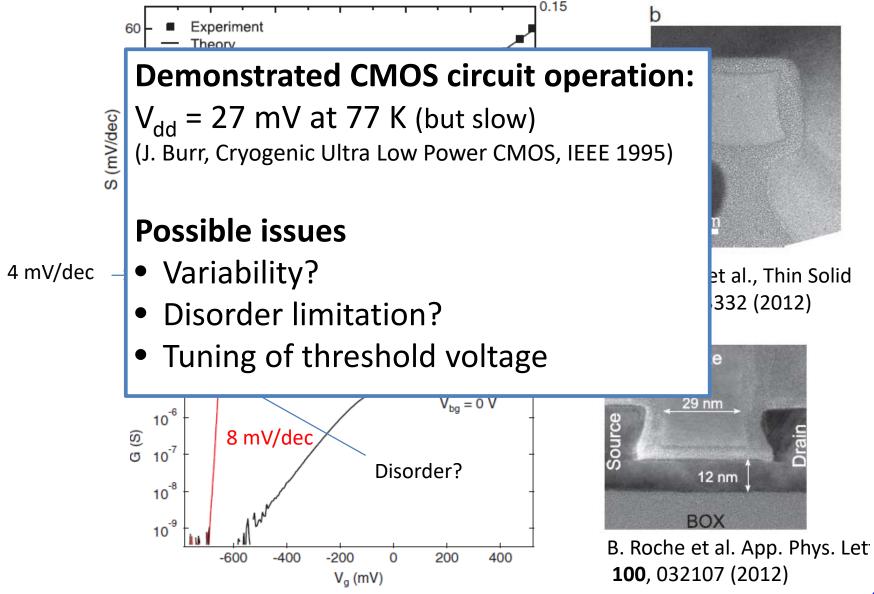

### **Useful Circumstances**

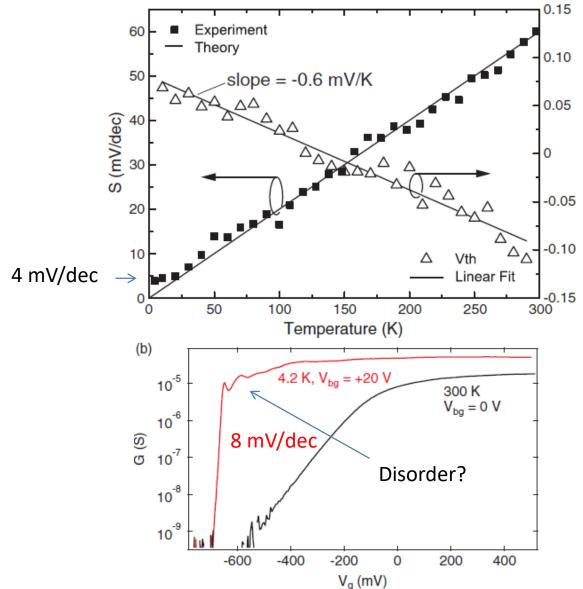

- Operation at  $\leq$  1 K => S = 0.2 mV/decade (Thermal limit. Disorder ?) => High mobility Use  $V_{dd} \approx$  10 mV (set by required output amplitude and speed)

- => Could operate at  $10^{-10}$  W per transistor (at f = 1 GHz, C = 1 fF)

- Low leakage

- Purely capacitive loads (~ fF scale) a few microns away

No power-hungry signal transmission

- Superconducting wires

=> Low dissipation, good thermal barriers.

# **Steep Slope Transistors**

Threshold Voltage (V)

S. Habicht et al., Thin Solid Films **520**, 3332 (2012)

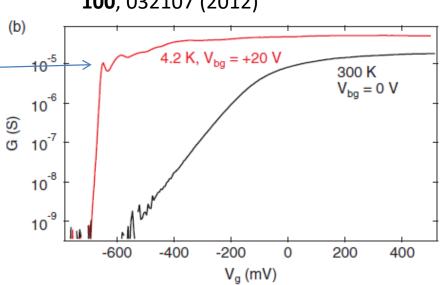

B. Roche et al. App. Phys. Let **100**, 032107 (2012)

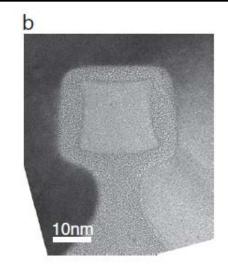

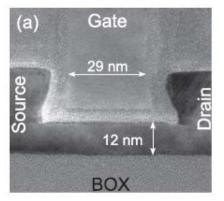

# **Steep Slope Transistors**

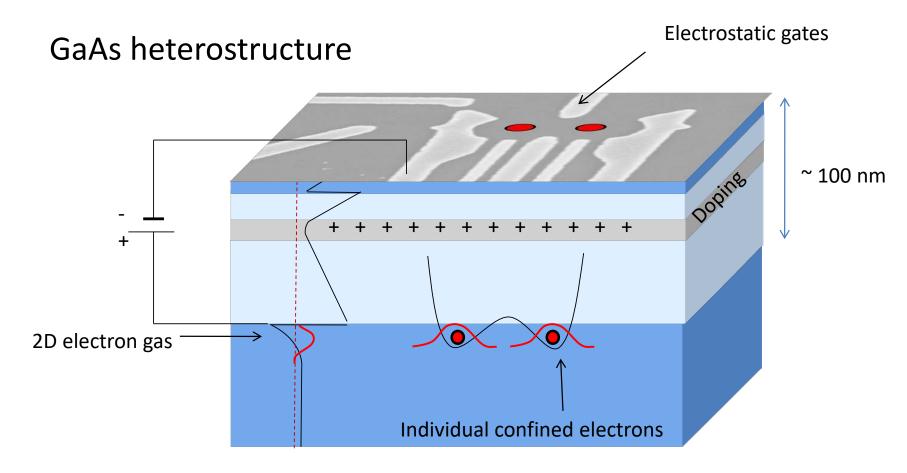

### Gate-defined Quantum Dots

Scalable top down fabrication with standard lithography

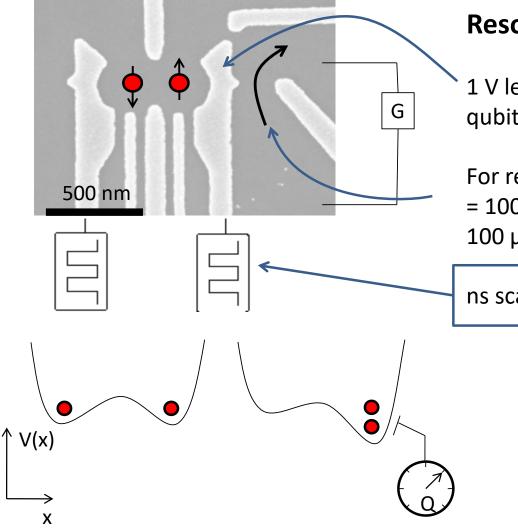

# Control of Two-electron Spin Qubits

### **Resources needed**

1 V level DC voltages to define and tune qubit

For readout: charge sensing =  $100 \text{ k}\Omega$  conductance measurement at  $100 \text{ \mu V} / 1 \text{ nA bias}$

ns scale, mV level gate pulses for control

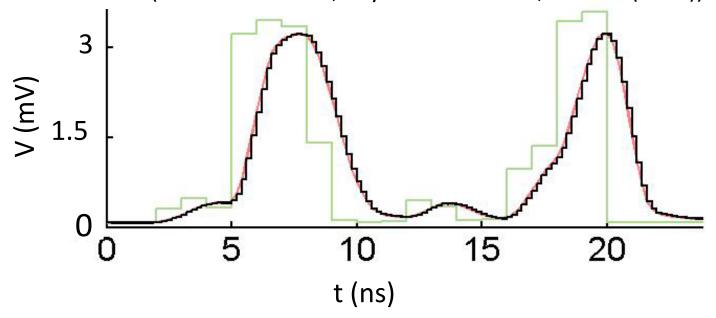

# Anatomy of a Control Pulse

### Exchange-mediated $\pi/2$ pulse

Programmed pulse

Experimental fidelity in GaAs: 98.5 % (arxiv:1606.01897). \_\_\_\_\_ Actual pulse Simulation: **99.8** % (Cerfontaine et al., Phys. Rev. Lett. **113**, 150501 (2014)).

**Hardware requirements:**

1 GS/s (could be reduced to ~ 300 MS/s)

5 mV output

~ 8 bit resolution

~ 16 samples per gate

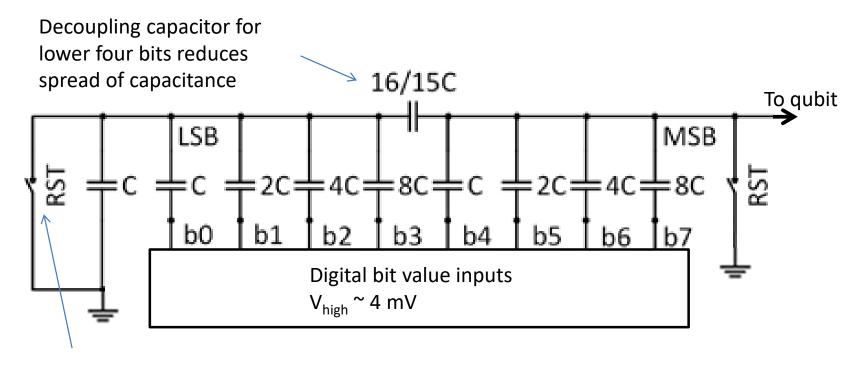

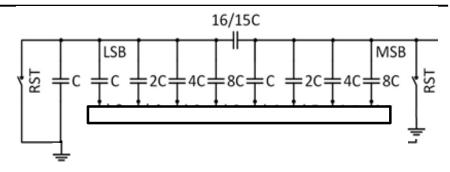

### Low Power DAC Concept

### Capacitive voltage division

- No quiescent current

- No need for large integrated resistors

- Less senstive to channel resistances than resistive division

Reset switches to compensate for leakage

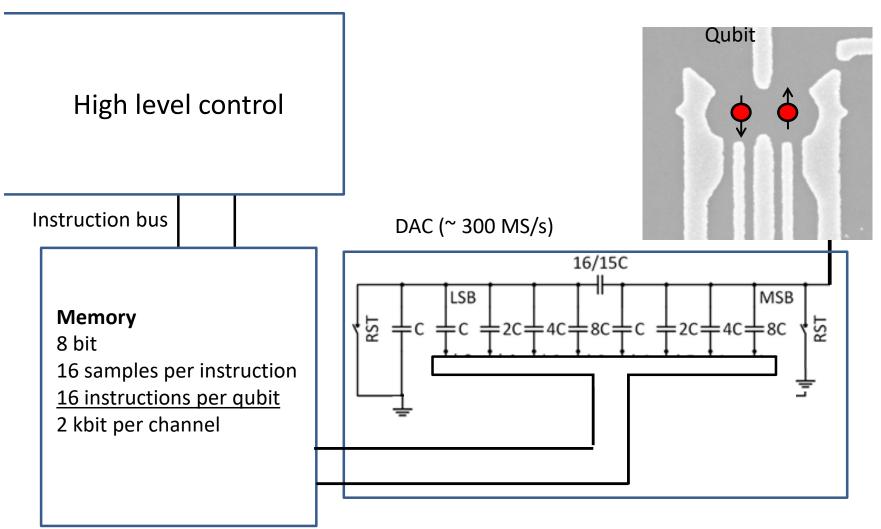

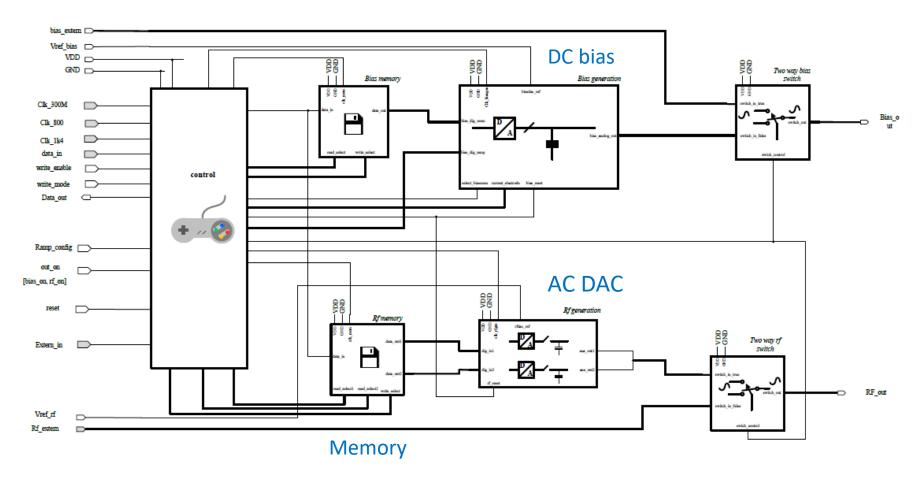

# **AC Control System**

All in ultra-low power cryogenic CMOS

# System Level Design Study

### Noise and Size

### Thermal noise

Output capacitance

$$= 16 C \ge \frac{k_B T}{\langle \delta V^2 \rangle} = 0.5 \text{ fF}$$

for 0.2 nV/Hz output noise and T = 0.2 K

Corresponds to 500  $\mu m^2$  with 2 fF/ $\mu m^2$  technology for DAC capacitors.

### **Transistor count**

37.000 in control unit

36.000 for 2 kBits of memory

$14.000 \, \mu m^2 = 120 \, x \, 120 \, \mu m$  at  $0.25 \, \mu m^2$  per transistor.

### => Unit nearly small enough

# **Power and Speed**

### Power dissipation (DAC only)

$$8 C f_{samp} V_{dd}^{2} = 2 \text{ nW}$$

at  $f_{samp} = 300 \text{ MS/s}, V_{dd} = 4 \text{ mV}$

### **Switching speed**

$R_{channel} = 100 \text{ k}\Omega$  —  $C_{max} = 4 C = 0.13 \text{ pF}$  =>  $\tau_{RC} = 13 \text{ ns}$

=> Needs factor 10 improvement compared to this unoptimized device

B. Roche et al. App. Phys. Lett **100**, 032107 (2012)

### Conclusion

- Integrated qubit control poses challenging but not impossible requirements on classical control circuits

- ~ 1 nW per qubit seems possible at low T seems possible, but requires a lot of rethinking, e.g.:

- -New transistors or different optimization targets

- -Specialized circuit designs

### Outlook

- Similar concept also suitable for DC bias

- Could potentially be extended to microwave Rabi control with ultra low power modulators

- => Applicable to other qubit types