This manuscript should be cited as IEEE Transactions on Applied Superconductivity, submitted 2008

# A Novel Power Line to Reduce the Magnetic Field of Supply Currents in Josephson Digital Circuits

Yuki Yamanashi, Theodore Van Duzer Life Fellow IEEE, Nobuyuki Yoshikawa Member IEEE

Abstract— One of the important issues facing the operation of large-scale Josephson digital circuits is that the dc supply currents are large and produce magnetic fields that have adverse effects. In this study, we have evaluated a novel patterning scheme for a superconductive twisted-pair bias supply line, which can reduce the static magnetic fields which adversely affect Josephson digital circuits. Several circuits have been designed and tested to evaluate the effectiveness of the twisted-pair bias supply lines, using the 2.5 kA/cm<sup>2</sup> SRL standard niobium process. Our experimental results indicate that the twisted-pair bias supply line can reduce substantially the static magnetic fields generated by the bias current. And it is demonstrated that the bias margin of large-scale Josephson circuits can be improved by using the novel bias supply lines. We believe that use of the twisted-pair will contribute, along with other techniques such as burying the bias lines under a thick ground plane, to the solution for the bias-current induced dc magnetic fields.

Index Terms—Bias current, Josephson junction, Single flux quantum circuit, Static magnetic fields

#### I. INTRODUCTION

Superconductive Josephson digital circuits are promising candidates for future integrated circuits because they can perform very high-speed circuit operation with ultra low-power consumption [1]. Many important digital circuits using Josephson junctions have been developed and experimentally demonstrated at high clock frequency [2], [3]. At present, the scale of Josephson circuits is much lower than that of semiconductor integrated circuits. To build practical digital systems using Josephson circuits, the integration level and the circuit scale must be increased drastically.

However, operations of very large scale Josephson circuits, containing more than 50,000 Josephson junction, have not yet been experimentally demonstrated. The most probable reason for the malfunctions is the effect of the static magnetic fields generated by dc bias current. Josephson digital circuits are very sensitive to external magnetic fields because they use single magnetic flux quanta in superconductive rings as carriers of the information. It has been pointed out that magnetic coupling between bias supply lines and superconductive loops in a

Manuscript received 19 August 2008.

circuit induces decreases the dc-bias margins of large-scale Josephson digital circuits [4]. Large-scale Josephson digital circuits, such as microprocessors, need bias currents of several amperes. To increase the integration level of Josephson digital circuits and ensure stable operation, the problem of bias-current -induced magnetic fields must be solved.

Various schemes have been devised to reduce the effects of the magnetic fields on circuit operation, such as an optimization of bias current distribution in large-scale SFQ circuits [5] and adopting superconducting shielding (SUSHI) structures in fundamental cells [6], and optimal moat design for trapping stray magnetic flux [7]. Among the schemes to reduce the static magnetic fields the most effective is using a thick ground plane covering the dc power lines [8]; we believe that this can be further enhanced by using a twisted-pair as the bias line. This complete scheme requires more superconducting layers than exist in the currently available Nb fabrication processes [9]. But it is expected that the process that will be used for very large circuits will necessarily have the additional layers.

As a preliminary demonstration of the value of the twisted-pair, we have fabricated this novel bias supply line without changing the existing fabrication process. The basic idea is using the twisted-pair commonly used in wired electronic circuits. We have devised a patterning scheme that produces the thin-film equivalent of the twisted-pair using the conventional Nb fabrication process. Our experimental results of the test circuits using the novel bias supply lines demonstrate the advantage over a parallel-wire line.

## II. SUPERCONDUCTIVE TWISTED PAIR

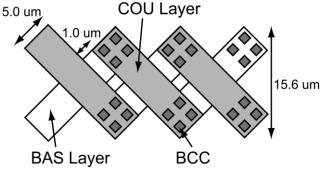

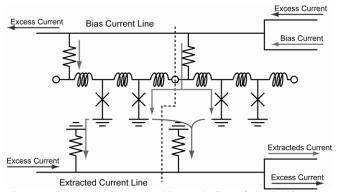

We have devised a patterning scheme that produces the equivalent of the twisted-pair using the conventional chip fabrication process. Fig. 1 shows the mask layout of the superconductive twisted-pair used in the test circuits described later. The superconductive twisted-pair is composed of two superconductive wiring layers, the BAS layer and the COU layer, separated by an insulating layer. The bias current is supplied to one line and the same current is extracted using the other line. The width of each wiring layer is 5  $\mu$ m. The similar scheme has been devised for printed circuits to reduce ac magnetic fields [10].

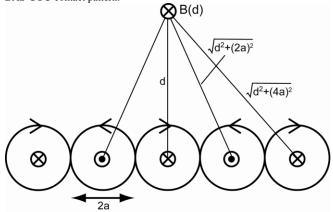

Fig. 2 shows a model of the superconductive twisted pair depicted in Fig. 1 to calculate the static magnetic fields. The equivalent series of circulating currents can be represented as a series of alternating magnetic dipoles. We can calculate the

Y. Yamanashi and N. Yoshikawa are with Yokohama National University, Yokohama 240-8501, Japan (e-mail: yamanasi@ynu.ac.jp).

T. Van Duzer is with University of California Berkeley, CA 94720-1770, USA (e-mail: vanduzer@eecs.berkeley.edu)

Fig. 1. Mask layout of the superconductive twisted pair. BCC means the BAS-COU contact pattern.

Fig. 2. Calculation model of the superconductive twisted pair. The equivalent series of circulating currents can be represented as a series of magnetic dipoles, a is the radius of each circulating current.

dependence of the magnetic fields on the distance from the center of the bias supply line. The magnetic field at a distance d from the center of circulating current  $I_b$ , the radius of which is a, can be represented as

$$B(d) \approx \frac{\mu_0 I_b a^2}{2d^3} \,, \tag{1}$$

assuming d >> a. Therefore, magnetic field generated by the series of alternating magnetic dipoles can be represented as

$$B(d) \approx \frac{\mu_0 I_b a^2}{2} \left[ \frac{1}{d^3} - \frac{2}{\left\{ d^2 + (2a^2) \right\}_2^{\frac{3}{2}}} + \frac{2}{\left\{ d^2 + (4a^2) \right\}_2^{\frac{3}{2}}} - \cdots \right]$$

(2)

From this calculation, the magnetic fields generated by the twisted-pair fall off as the third power of transverse distance from the twisted pair, whereas magnetic fields generated by a parallel-wire bias line decrease less rapidly with distance from the line. Therefore, using the superconductive twisted-pair as bias supply lines is expected to be effective in reducing the static magnetic fields produced by large bias currents on the circuit operation.

## III. MEASUREMENT OF STATIC MAGNETIC FIELDS

We have designed and tested some simple circuits to measure the dependence of the static magnetic fields generated by the superconductive twisted-pair on the distance from the twisted-pair using the SRL 2.5 kA/cm<sup>2</sup> Nb standard process

[11]. The test circuit is composed of a bias supply line using the twisted-pair and several dc-SQUIDs. The SQUID loop is designed using the CTL layer, the top layer of the SRL 2.5 kA/cm<sup>2</sup> Nb standard process. The length and width of the SQUID loop are 16 µm and 1.6 µm, respectively. The designed critical current of the dc-SQUID is 200 µA. Static magnetic fields can be measured as a function of distance from the twisted pair from 0 µm to 15 µm. We have also designed the same test circuits using a vertically stacked parallel-wire bias line instead of the twisted pair. The parallel line also uses the BAS and COU layers. The line width of each layer is 5 µm and two layers completely overlap. By comparing experimental results of two test circuits, we have evaluated the effectiveness of the twisted-pair bias supply line. We have measured threshold current of each SOUID as a function of supply bias current I<sub>b</sub>.

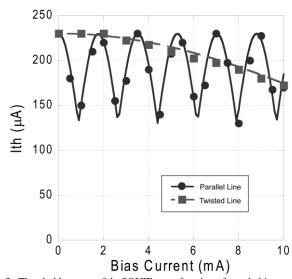

Fig. 3 shows an example of threshold curve of the dc-SQUID lying directly above the bias lines. It is seen that there is very little modulation in the case of the twisted pair whereas there is substantial modulation in the parallel conductor line. It is important to note that the measuring SQUID is larger than the

Fig. 3. Threshold current of dc-SQUIDs as a function of supply bias current. Distance between the bias line and the dc-SQUID is 0  $\mu$ m. Dots are measured values and solid/dashed lines are fitting curves.

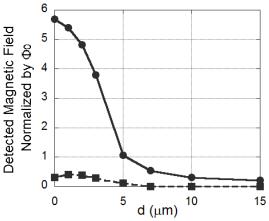

Fig. 4. Dependence of the magnetic flux measured by the dc-SQUIDs on the distance from the bias line. Measured magnetic flux is normalized by the flux quantum  $(\Phi_0)$ . The bias line current is 10 mA.

Fig. 5. Equivalent circuit including bias supply lines of tested shift register (SR). The dashed line corresponds to the boundary of cell. Bias current line and extracted current line compose the twisted pair.

diameter of the circulating currents in Fig. 2 and may be averaging the fields of the counter-rotating currents. As seen in Fig. 4, for all values of the spacing d, the modulations of threshold curves of the dc-SQUIDs are smaller with the twisted-pair than in the case with the vertically stacked parallel line. Furthermore, we have found that, with  $I_b = 10$  mA, there is no modulation of the characteristic of the dc-SQUID when the twisted bias line is used and the d is more than 7 µm, while clear modulations are observed in the case of measurements of the conventional parallel bias line. Measured magnetic flux is estimated from fitting curves of the type shown in Fig. 3. This result indicates the twisted bias supply line can reduce the effective static magnetic field generated by bias currents to less than 1/10 even just above the bias lines compared to the conventional bias line. This result indicates the magnetic fields are cancelled by alternating magnetic dipoles, though the d-3 dependence is not shown because the assumption, d>> a, is not satisfied in this region.

# IV. EFFECT ON MARGINS

We have designed and tested an 8-bit counter-flow shift register to evaluate the effectiveness of the superconductive twisted pair as the bias supply line in practical circuits. To realize a two-conductor supply line, extracted currents are used in this shift register. Fig. 5 shows the equivalent circuit of the designed shift register. Bias currents are supplied to the circuit using an off-chip voltage source and on-chip bias resisters. And supplied bias currents are extracted from the ground plane by on-chip resisters and applying negative voltage to the extracted bias line. Bias current line and extracted current line compose the twisted pair. Furthermore, bias currents can be concentrated in the circuit by supplying excess current to the bias and extracted lines as shown in Fig. 5 to imitate large-scale circuits. The number of Josephson junctions and bias current of the designed 8-bit shift register are 136 and 17.7 mA, respectively. Though the circuit scale of the shift register is very small, the shift register can imitate the large-scale circuits by supplying excess current to the circuit.

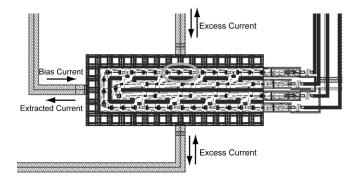

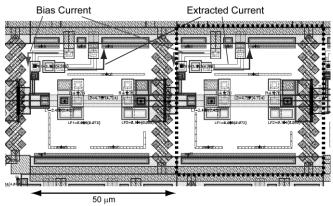

Fig. 6 shows a mask layout of the designed shift register using the superconductive twisted pair. Fig. 7 shows the expansion of the layout indicated by an oval in Fig. 6. The

Fig. 6. Mask layout of the tested shift register using twisted bias supply lines. Excess bias current is supplied and extracted using two bias supply ports. The width of each current line is 20  $\mu m$ . Squares in the shift register correspond to fundamental cells. The circuit size of each fundamental cell is  $50~\mu m \times 50~\mu m$ .

Fig. 7. Expansion of the mask layout indicated by a circle in Fig. 6. The area surrounded by a dashed square corresponds to JTL (Josephson transmission line) cell.

width of the twisted bias lines is 2 µm in this test circuit. Signal lines, designed using the CTL layers, cross the twisted bias supply lines as shown in Fig. 7. Bias supply lines, which don't cross over twisted bias supply lines and correspond to horizontal bias lines in Fig. 7, are composed of vertically stacked parallel-wire and are completely shielded by covering the bias lines using CTL shield layers. Therefore, bias supply line and circuit are coupled only at the intersections of signal lines and twisted pairs. Bias current and extracted currents are supplied and extracted by vertically stacked bias lines to the circuits as shown in Fig. 6. Excess current are also supplied and extracted by different stacked bias lines.

We also designed the same shift register using vertically stacked parallel-wire bias line in place of the twisted-pair lines. We have measured the dc bias margin of each shift register and compared the measurement results.

# V. RESULTS AND DISCUSSION

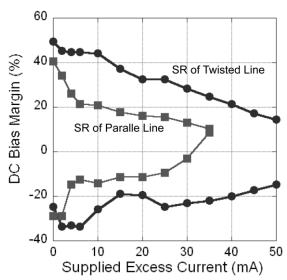

Fig. 8 shows the measured dc bias margin of each shift register. The dc bias margin shrinks with increases of the excess currents because the magnetic fields generated by the excess current induce malfunctions of the shift register. The dependence of the dc bias margin of the shift register, which uses twisted pair bias lines, on the excess bias current is smaller than in the case of the parallel bias supply line.

Fig. 8. Measured dc bias margins of two shift registers (SRs).

However, the effects of reduction of magnetic fields by using the twisted pair are smaller than expected from the results described in Fig. 4. This may be because the radius of circulating current in the series of magnetic dipole in the twisted pair is not small compared to the size of the circuit. By minimizing the size of the twisted pair, more effective cancellation of the static magnetic fields is possible. And by using the shielding of the bias supply line, we can drastically reduce the effects of magnetic fields generated by the bias currents.

# VI. CONCLUSION

We have devised a patterning scheme to realize superconductive twisted pairs in Josephson integrated circuits to reduce the effects of the magnetic fields generated by bias currents. We have designed and measured several test circuits to evaluate the novel bias supply line. Experimental results indicate that static magnetic fields generated by the bias current can be reduced substantially by using the twisted pair as the

bias supply line. The dc bias margin of the measured circuit remains relatively large even if the concentration of the bias currents occurs. We believe that use of the twisted-pair will contribute, along with other techniques such as burying the bias lines under a thick ground plane, to the solution for the bias-current induced dc magnetic fields.

#### REFERENCES

- K. K. Likharev and V. K. Semenov, "RSFQ logic/memory family: A new Josephson-junction digital technology for sub-terahertz-clock-frequency digital systems," *IEEE Trans. Appl. Supercond.*, vol. 1, pp. 3–28, Mar. 1991.

- [2] O. Mukhanov, D. Gupta, A. Kadin, and V. K. Semenov, "Superconductor Analog-to-Digital Converters," *Proceedings of the IEEE*, vol. 92, pp. 1564-1584, Oct. 2004.

- [3] Y. Yamanashi, M. Tanaka, A. Akimoto, H. Park, Y. Kamiya, N. Irie, N. Yoshikawa, A. Fujimaki, H. Terai, and Y. Hashimoto, "Design and Implementation of a Pipelined Bit-Serial SFQ Microprocessor, CORE1beta," *IEEE Trans. Appl. Supercond.*, vol. 17, pp. 474-477, Jun. 2007.

- [4] M. Suzuki, M. Maezawa, and F. Hirayama, "Effects of magnetic fields induced by bias currents on operation of RSFQ circuits," *Physica C* 412-414, pp. 1576-1579, Jun. 2004.

- [5] Y. Yamanashi, K. Kawasaki, N. Yoshikawa, H. Terai, A. Fujimaki, Y. Kameda, and S. Yorozu, "A Calculation of Bias Current Distribution in Large-Scale SFQ Logic Circuits" in *Int. Supercond. Elect. Conf.*, Sydney, Australia, Jul. 2003.

- [6] N. Yoshikawa, T. Nishigai, H. Kojima, K. Fujiwara, A. Fujimaki, T. Yamada, M. Tanaka, S. Yorozu, M. Hidaka, and H. Terai, "Magnetic shielding against DC bias current toward large-scale SFQ integrated circuits," in *Appl. Supercond. Conf.*, Jacksonville, FL, Oct. 2004.

- [7] M. Jeffery, T. Van Duzer, J. R. Kirtley, and M. B. Ketchen, "Magnetic Imaging of Moat-Guarded Superconducting Electric Circuits," *Appl. Phys. Lett.*, vol. 67, pp. 1769-1771, Sep. 1995.

- [8] H. Akaike, A. Fujimaki, S. Nagasawa, Y. Kitagawa, and M. Hidaka, "Effects of the film thickness of a ground plane in the SFQ circuits with a dc-power layer," *Supercond. Sci. Technol.*, vol. 20, pp. S336-340, Oct. 2007.

- [9] S. Nagasawa, K. Hinode, T. Satoh, H. Akaike, Y. Kitagawa, and M. Hidaka, "Development of advanced Nb process for SFQ circuits," *Physica C*, vol. 412-414, pp. 1429-1436, Jun. 2004.

- [10] It has come to our attention that planar twisted pairs have been used in printed circuit boards. Ref. U.S. Patent No. 5646368: "Printed circuit board with an integrated twisted pair conductor" 7/8/1997.

- [11] S. Nagasawa, Y. Hashimoto, H. Numata, and S. Tahara, "A 380 ps, 9.5 mW Josephson 4-kbit RAM operated at a high bit yield," *IEEE Trans. Appl. Supercond.*, vol. 5, pp. 2447–2452, Jan. 1995.